计算机体系结构分类与存储系统

计算机体系结构分类

(1)按处理机的数量进行分类:

- 单处理系统

- 并行处理与多处理系统

- 分布式处理系统

(2)微观上按并行程度分类:Flynn分类法、冯泽云分类法、Handler分类法等等

CISC和RISC

RISC全称Reduced Instruction Set Compute,精简指令集计算机。

CISC全称Complex Instruction Set Computers,复杂指令集计算机。

| 对比项 | CISC(复杂指令集) | RISC(精简指令集) |

|---|---|---|

| 指令集复杂度 | 指令集庞大且复杂,单条指令可执行多个操作(如内存访问、运算等) | 指令集精简且统一,每条指令仅执行单一操作,复杂功能由简单指令组合实现 |

| 指令长度 | 变长指令,灵活但解码复杂 | 固定长度指令,解码简单且易于流水线处理 |

| 执行时间 | 单条指令可能需要多个时钟周期完成 | 大多数指令在一个时钟周期内完成,采用流水线技术提升效率 |

| 硬件设计 | 硬件复杂度高,需支持多种指令操作,通常采用微程序控制 | 硬件设计简单,多采用组合逻辑控制,易于集成流水线和超标量技术 |

| 寄存器数量 | 寄存器数量较少,频繁访问内存 | 通用寄存器数量多,减少内存访问,操作主要在寄存器间完成 |

| 寻址方式 | 支持多种复杂寻址模式(如间接、基址、索引等) | 寻址方式简单,通常仅支持少数基本模式(如寄存器、立即数等) |

| 编译器优化 | 编译器优化难度大,但生成代码紧凑 | 编译器优化容易,但代码量可能较大 |

| 应用场景 | 适用于通用计算(如桌面PC、服务器),强调向后兼容性 | 适用于高效能低功耗场景(如移动设备、嵌入式系统) |

| 典型代表架构 | x86(Intel/AMD) | ARM、MIPS、RISC-V2 |

| 功耗与能效 | 功耗较高,能效比相对较低 | 功耗低,能效比高 |

| 中断响应 | 在指令执行结束后响应中断 | 可在指令执行过程中适当时机响应中断 |

流水线技术

流水线周期:一个指令中,时间最费时(最慢)的子任务时间

串行执行时间:N*一个指令总时长

流水线执行时间:一条指令时长+(N-1)*流水线周期

吞吐量:p=1/流水线周期

存储系统

分类

1、存储器的分类:

- 按存储器所处的位置:可分为内存和外存。

- 按构成存储器的材料:可分为磁存储器、半导体存储器和光存储器。

- 按存储器的工作方式:可分为读写存储器和只读存储器。

- 按访问方式:可分为按地址访问的存储器和按内容访问的存储器。

- 按寻址方式:可分为随机存储器、顺序存储器和直接存储器。

2、随机访问存储器:

- 静态随机访问存储器(SRAM)

- 动态随机访问存储器(DRAM)

3.高速缓存

- Cache是介于CPU与主存之间的一级存储器,其容量较小,但速度较快,一般比主存快5~10倍。

- 它的主要作用是:调和CPU的速度与内存存取速度之间的差异,从而提升系统性能。

- 它使用的是程序的局部性原理,其内容是主存局部域的副本。

- 当CPU需要读取数据时,首先判断要访问的信息是否在Cache中,如果在即为命中,如果不在,就要按替换算法把主存中的一块信息调入Cache中。

- 替换算法有:随机替换算法、先进先出替换算法、近期最少使用替换算法、优化替换算法等。

- CPU工作时给出的是主存的地址,要从Cache存储器中读写信息,就需要将主存地址转换成Cache存储器的地址,这种地址的转换叫作地址映像。

4.虚拟存储器、相联存储器

- 虚拟存储器实际上是一种逻辑存储器。

- 相联存储器是一种按内容访问的存储器。

地址映射

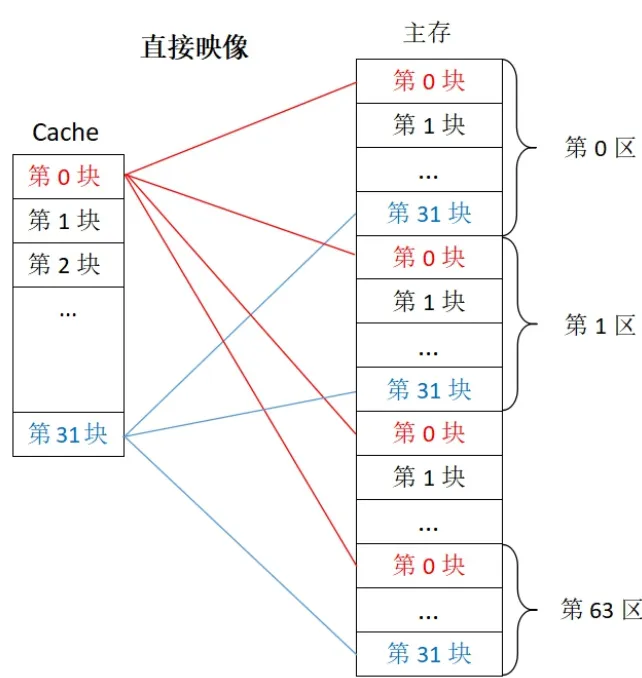

直接映射

主存的块与Cache块的对应关系是固定的,主存中的块只能存放在Cache存储器的相同块号中。

优点:地址变换简单、访问速度快。

缺点:块冲突率高、Cache空间得不到充分利用。

主存地址:主存区号 | 区内块号 | 块内地址

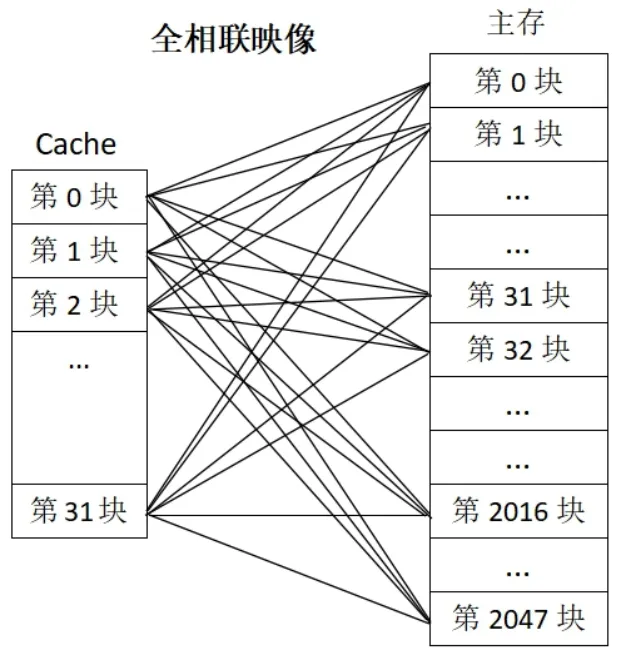

全相联映射

主存与Cache存储器均分成容量相同的块。允许主存的任一块可以调入Cache存储器的任何一个块的空间中。

优点:灵活,块冲突率低,只有在Cache中的块全部装满后才会出现冲突,Cache利用率高。

缺点:无法从主存块号中直接获得所对应Cache的块号,变换比较复杂,地址变换速度慢,成本高。

主存地址:主存块号 | 块内地址

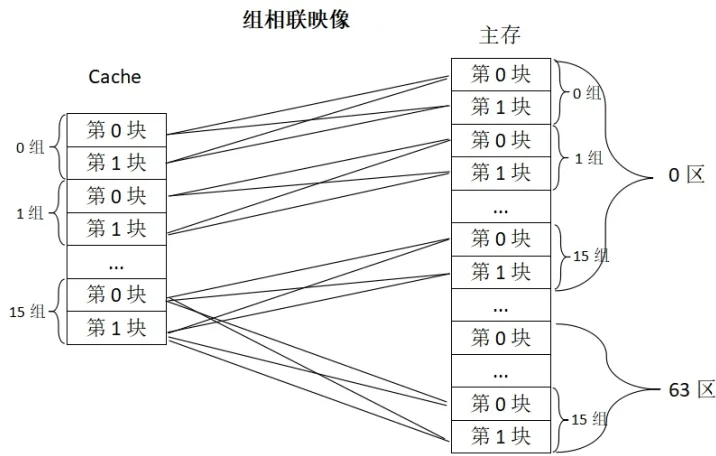

组相联映像

是前两种方式的折衷。

将Cache中的块再分成组(分块、分组)。组采用直接映像方式而块采用全相联映像方式。

主存的任何区的0组只能存Cache的0组中,1组只能存放到1组中,依此类推。而组内的块可以存入Cache中相同组的任一块中

主存地址位数=区号+组号+主存块号+块内地址

Cache地址位数=组号+组内块号+块内地址

性能分析

Cache的性能分析:

设Hc为Cache的命中率,tc为Cache的存取时间,tm为主存的访问时间,则Cache存储器的等效加权平均访问时间ta为:

编址相关计算

内存单元按字节编址

存储单元数量 = 末地址-首地址+1